cache是什么意思? cache三大部分組成介紹

在計算中,高速緩存(cache)是存儲數據的硬件或軟件組件,以便可以更快地滿足對該數據的將來請求。存儲在緩存中的數據可能是早期計算的結果,也可能是存儲在其他位置的數據的副本。

CPU高速緩存是由計算機的中央處理器(CPU)使用的硬件緩存,用于降低從主內存訪問數據的平均成本(時間或能量)。緩存是一種更小、更快的內存,位于更靠近處理器核心的位置,存儲來自經常使用的主內存位置的數據副本。

高速緩沖存儲器是存在于主存與CPU之間的一級存儲器, 由靜態存儲芯片(SRAM)組成,容量比較小但速度比主存高得多, 接近于CPU的速度。

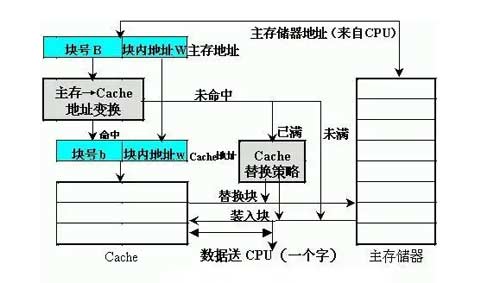

主要由三大部分組成:

Cache存儲體:存放由主存調入的指令與數據塊。

地址轉換部件:建立目錄表以實現主存地址到緩存地址的轉換。

替換部件:在緩存已滿時按一定策略進行數據塊替換,并修改地址轉換部件。

大多數cpu都有不同的獨立緩存,包括指令緩存和數據緩存,其中數據緩存通常組織為多個緩存級別(L1、L2、L3、L4等)的層次結構。

所有現代(快速)CPU(除了少數特殊的例外)都有多個級別的CPU緩存,第一個使用緩存的cpu只有一級緩存。與后來的一級緩存不同,它沒有被分成L1d(用于數據)和L1i(用于指令)。

分離式L1高速緩沖存儲器始于1985年的R2000 MIPS處理器,1993年的英特爾奔騰處理器成為主流,1997年的ARMv5TE處理器成為嵌入式CPU市場的主流。在2015年,甚至低于美元的SoC也分裂了L1緩存。

它們還有L2緩存,對于較大的處理器,還有L3緩存。L2緩存通常不被分割,它充當已經分割的L1緩存的公共存儲庫。多核處理器的每個核心都有一個專用的L1緩存,通常不會在核心之間共享。

L2緩存和更高級的緩存可以在核心之間共享,L4緩存目前并不常見,通常是在(一種形式的)動態隨機訪問內存(DRAM)上,而不是在靜態隨機訪問內存(SRAM)上,在一個單獨的die或chip上(例外情況下,該形式的eDRAM用于從L1到所有級別的緩存)。

歷史上L1也是這種情況,而更大的芯片允許集成它和所有的緩存級別,最后一層可能除外。每一個額外的緩存級別都趨向于更大,并以不同的方式優化。

存在其他類型的緩存(它們不計入上面提到的最重要的緩存的“緩存大小”),比如translation lookaside buffer (TLB),它是大多數cpu擁有的內存管理單元(MMU)的一部分。

緩存(如歷史上的RAM)的大小通常是2、4、8、16等。簡約;當達到MiB大小(即更大的非l1)時,該模式很早就被打破了,以允許更大的緩存,而不必被迫采用雙倍大小的模式,例如2008年4月Intel Core 2 Duo與3 MiB L2緩存。

然而L1大小,很久以后仍然只數在小數量的簡約,然而IBM zEC12從2012年是一個例外,96年獲得極大的簡約L1數據緩存的時間,如IBM z13有96簡約L1指令緩存(128簡約L1數據緩存)和英特爾冰Lake-based處理器從2018年開始,有48個簡約L1數據緩存和48簡約L1指令緩存。